ARM嵌入式系统

1 基于ARM的嵌入式系统

在这一章讨论ARM是如何采用RISC设计了一个灵活的嵌入式处理器;然后通过介绍一个嵌入式设备的实例,讨论围绕ARM处理器的典型的软硬件技术。

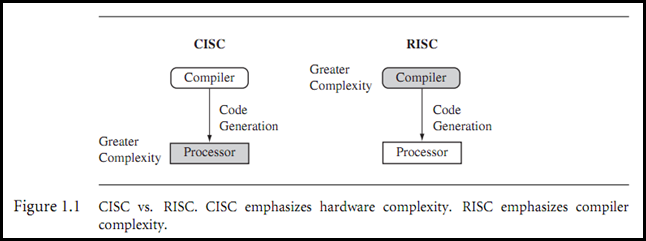

1.1 RISC设计思想

ARM采用RISC体系结构。RISC的目标在于设计出一套能在高时钟频率下单周期执行,简单而有效的指令集。RISC的设计重点在于降低硬件执行指令的复杂度,因为软件比硬件能提供更高的灵活性和更高的智能。因此,RISC对编译器有更高的要求。

RISC的设计思想主要由以下4个准则来实现:

(a)RISC指令集:使用定长的、简单的、种类少的指令。

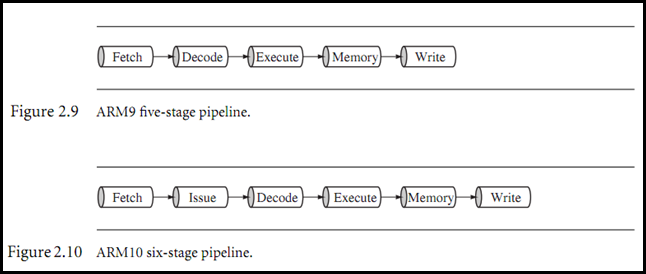

(b)Pipeline

(c)Register:RISC拥有更多的通用的寄存器。而CISC都是用于特定目的的专用寄存器。

(d)load-store结构:处理器只处理寄存器中的数据。独立的load、store指令用来完成数据在寄存器和外部存储器之间的传送。

1.2 ARM设计思想

低功耗:嵌入式设备的要求。

高代码密度:存储器容量限制。

低成本:嵌入式设备对于价格敏感。

小面积:缩小嵌入式处理器内核管芯的面积。对于一个SOC,管芯的面积越小,留给外围电路的空间就越大。

硬件调试技术:使软件工程师能够观察到处理器执行指令的情况。

1.2.1 ARM嵌入式指令集

为了更好适应需要,ARM指令集和纯粹的RISC有如下区别:

(a)一些特定指令执行的周期可变.

(b)内嵌桶形移位器产生了更复杂的指令,如add r0,r2,lsl 3

(c)Thumb 和Thumb2指令。

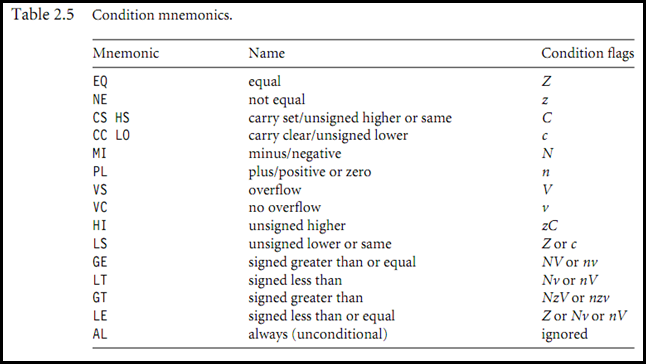

(d)条件执行,如moveq.

(e)增强指令:如乘除法指令。

1.3 嵌入式系统的硬件

下图是一个典型的ARM嵌入式SOC.一个方框代表一个功能块。方框之间的连线是总线。

可以把SOC分成以下4个部分:

(a)ARM处理器--控制整个器件.一个ARM处理器包含了一个内核,以及片内的存储器如TCM、Cache等。

(b)控制器:如存储器控制器,LCD 控制器,中断控制器。

(c)外设:提供芯片与外部的所有输入输出功能。MIC、CODEC等。

(d)总线:数据传输

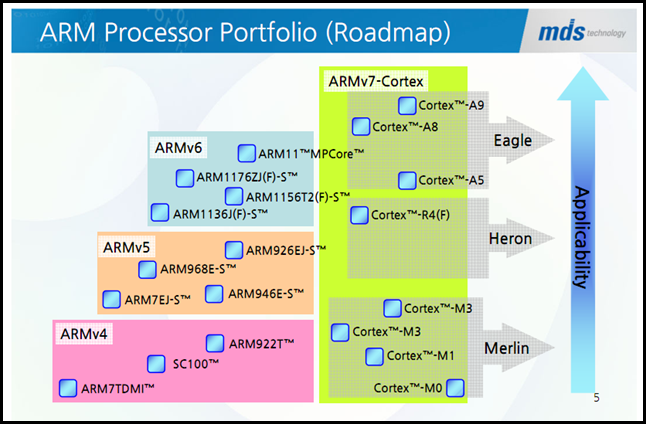

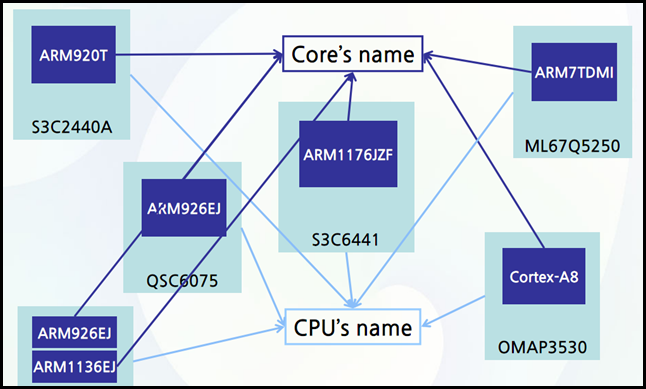

以下2个图分别是ARM core的roadmap,和一些使用ARM core搭建的ARM processor的示例。

1.3.1 ARM总线设计技术

总线可分为2个结构层:第一层是物理层,定义电气特性;第二层是协议层,定义通信的逻辑规则。

ARM不涉及总线的电气特性,但详细定义了协议层。

1.3.2 AMBA总线协议

AMBA(Advanced Microcontroller Bus Architecture).最初的AMBA包括ASB(Arm System Bus)和APB(Arm Peripheral Bus),后来ARM提出的AHB(ARM High Performance Bus)替代了ASB.后来AHB引入了2个变体:多层AHB和AHB-Lite。前者允许多个活动的主设备同时在总线上。

1.3.3 存储器

存储器的设计和选择时,必须综合考虑价格、功耗、存储效率。

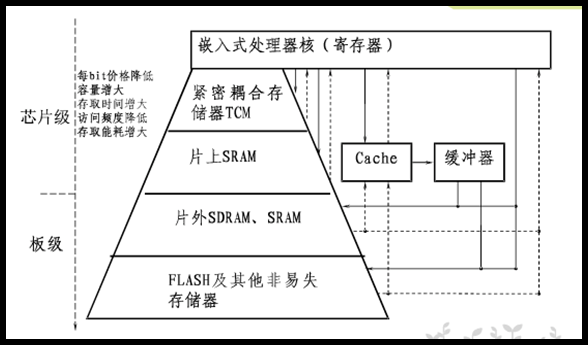

1.3.1 存储器的层次

按从上到下的顺序:(a)每bit价格降低;(b)容量增大;(c)访问速度慢;(d)访问频度降低;(e)存取能耗大

1.3.2 存储器的数据宽度

存储器宽度即访问一次存储器,获取到的数据的宽度,典型的有8/16/32/64位。最好让指令宽度和存储器宽度一致。

1.3.3 存储器类型

ROM:用来存储生产后就不可变更的内容。

Flash:可读写,但是慢。cpu无法直接访问Flash上的内容,必须先把数据搬到SDRAM或者RAM中,才能被load指令访问。

DRAM:价格最低。需要动态刷新,不断给电容充电。

SRAM:无需动态刷新,存取速度快,但是贵,为什么贵得看下每个存储单元的电路图。

SDRAM:能比普通的存储器工作在更高的时钟频率下。因为SDRAM使用时钟,所以他和处理器总线是同步的。数据从存储单元被流水化地取出,最后突发式地输出到总线。

1.3.4 外设

所有ARM外设都是存储器映射的,就是统一编址。

1.3.4.1存储器控制器

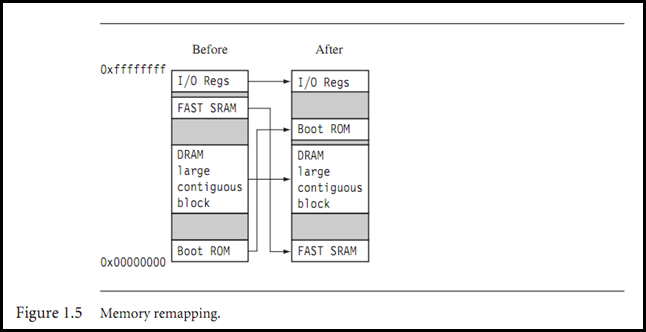

各种不同的存储器通过存储器控制器连接到总线上。上电时,存储器通过硬件配置,使得某些存储器处于工作状态,如SRAM和ROM,这些存储器允许执行初始化代码。有些存储器必须在使用之前通过软件设置,如SDRAM。

1.3.4.2 中断控制器

分标准的中断控制器和向量中断控制器。

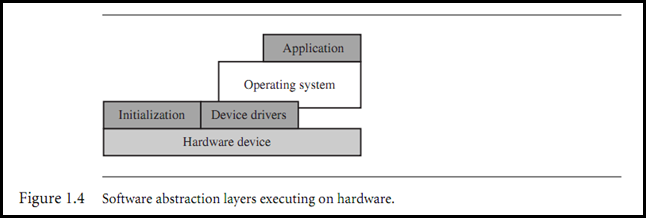

1.4 嵌入式系统的软件

1.4.1 bootloader(初始化代码)

bootloader的详细过程见http://blog.csdn.net/evanwu_85/archive/2010/10/22/5957777.aspx

下面仅贴出bootloader的一级loader运行完后,memory remap的图示。

1.4.2 操作系统(略)

1.4.3 应用程序 (略)

2 ARM处理器基础

2.1 寄存器(略)

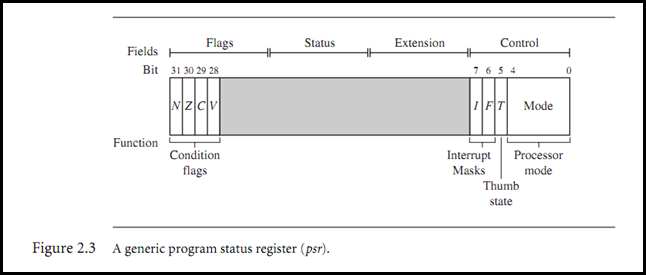

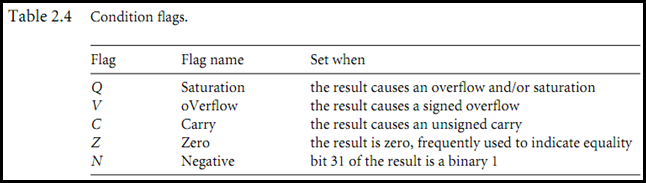

2.2 CPSR

ARM内核使用CPSR监视和控制内部操作。cpsr分4个8位区域:标志域、状态域、扩展域、控制域。目前扩展和控制域保留,供将来使用。控制域包含处理器模式、状态和中断屏蔽位;标志域包含条件标志位。

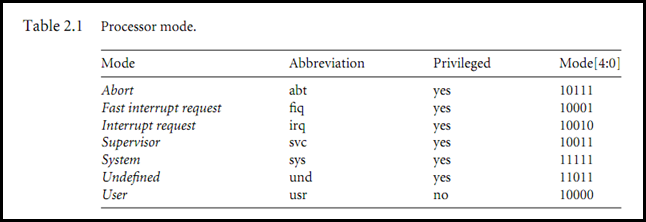

2.2.1 处理器模式

处理器模式决定哪些寄存器是处于活动的,以及对CPSR的访问权限。特权模式允许对CPSR进行读写操作,非特权模式只能进行写操作。

共有6种特权模式:abort、irq、fiq、supervisor、system、undefine;一种非特权模式:User。

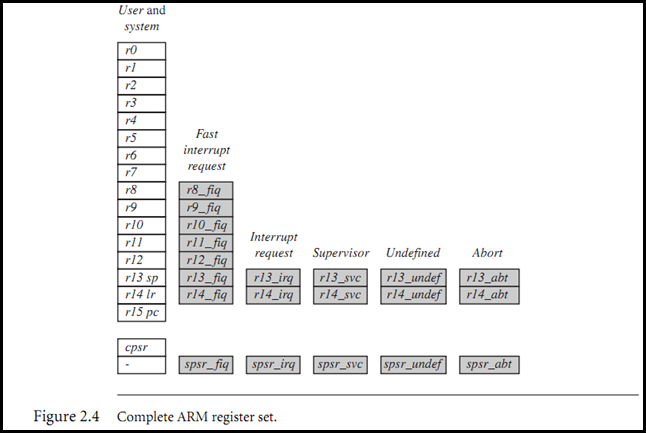

2.2.2 ARM寄存器组

除user模式外,其他的所有模式都可以通过改写cpsr来进行模式切换。除系统模式外,其他所有模式都有自己的一组寄存器。系统模式将复用user模式所有的寄存器,可以认为系统模式是一种特殊的user模式,一般没什么用。

处理器既可以通过改变cpsr来改变模式(处于特权模式下时),也可以当内核对异常或中断响应时由硬件切换。下面的异常和中断会导致模式切换:reset、irq、fiq、SWI、data abort、prefetch abort、undefined instructions。

当因中断或异常而发生状态切换时,CPSR会被保存到切换后模式的SPSR中。当因直接修改CPSR发生模式切换时,CPSR不会被保存。

(a)CPSR的低5位代表处理器模式,如下表所示:

(b)位5(T)置位表示处于ARM状态,为0则为Thumb状态。

(c)位7和位6(I和F),分别控制IRQ和FIQ的中断屏蔽,置位时中断被屏蔽。

(d)Condition flags高4位(N,Z,C,V).

2.2.3 条件执行

2.3 Pipeline

2.4 异常、中断和向量表

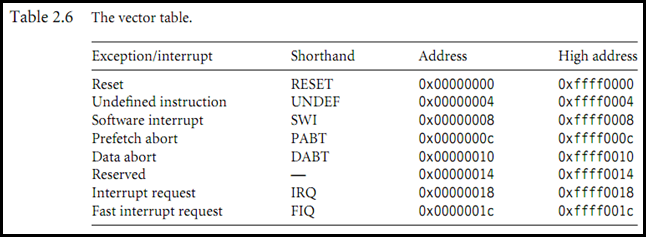

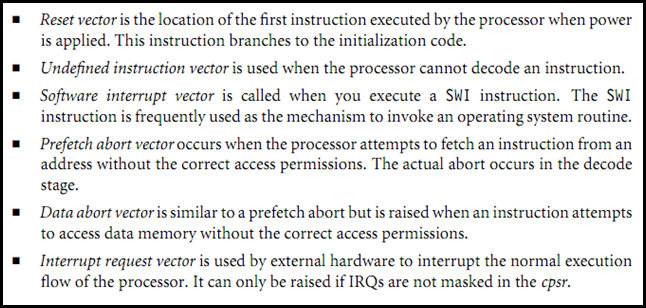

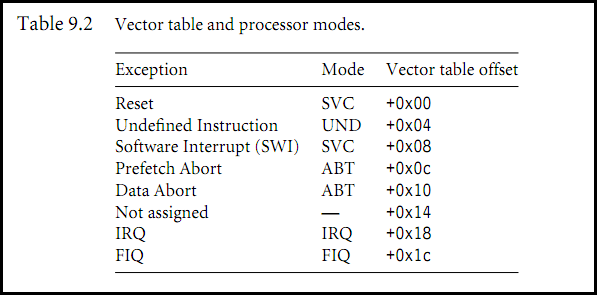

当一个中断或异常发生时,PC会被设到中断向量表里的某一个地址,这个地址就是相应异常或中断处理程序的入口地址。这个地址通常是一条跳转指令。大多数情况下,0x00000000地址是为向量表保留的。

2.5 内核扩展

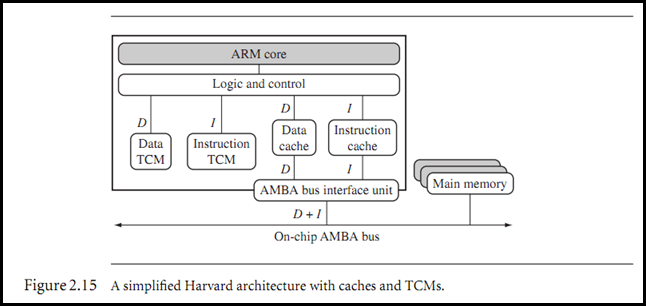

有3种硬件扩展位于内核周围:Cache和紧耦合存储器TCM、存储管理及协处理器接口。

2.5.1 Cache和TCM

Cache执行时间不可预测,对程序员不可见,不可寻址;TCM执行时间可预测,可寻址。

2.5.2 MMU和MPU

MMU:有保护,有映射

MPU:有保护,无映射

2.5.3 协处理器

协处理器可以附属于ARM处理器。一个协处理器通过扩展指令集或配置寄存器来扩展功能。一个或多个协处理器可以通过协处理器接口与ARM内核相连。

2.6 体系结构的不同版本

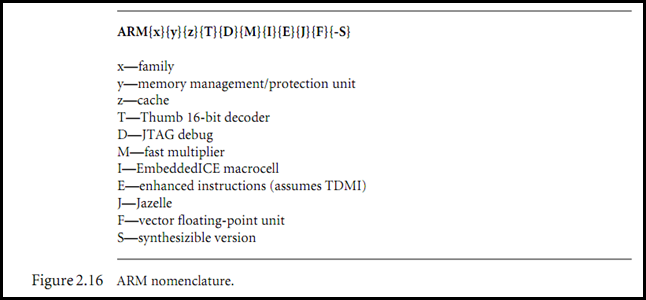

2.6.1 命名规则

关于ARM处理器的命名规则,还有一些附加的要点:

(a)ARMTDMI后所有的内核,即是“ARM”标志后没有包含那些字符,也具有TDMI的特性。

(b)处理器系列是共享硬件特性的一组处理器的具体实现。

(c)嵌入式ICE宏单元是建立在处理器内部、用来设置硬件断点的调试硬件。

(d)可综合的,意味着处理器内核是以源代码形式提供的。这种源代码形式又可以被编译成易于EDA工具使用的形式。

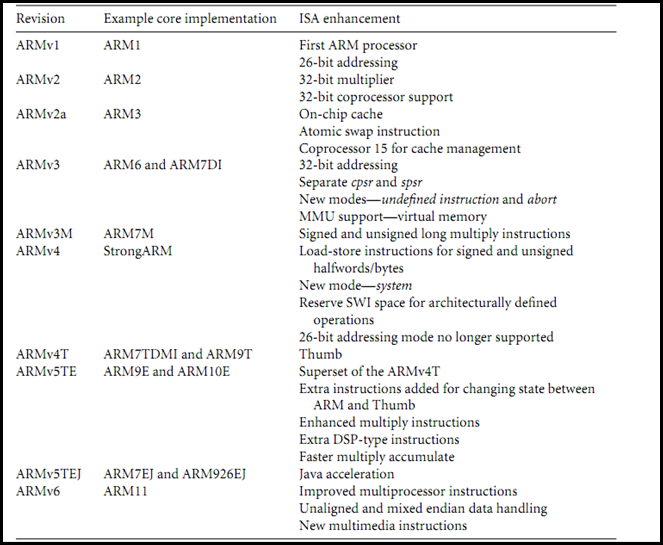

2.6.2 体系结构的发展

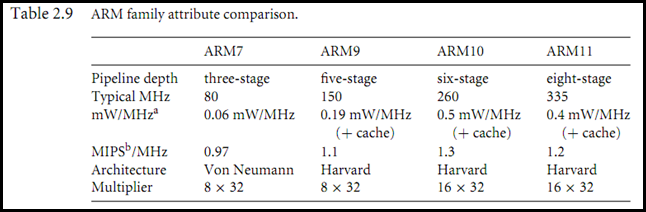

2.7 ARM处理器系列

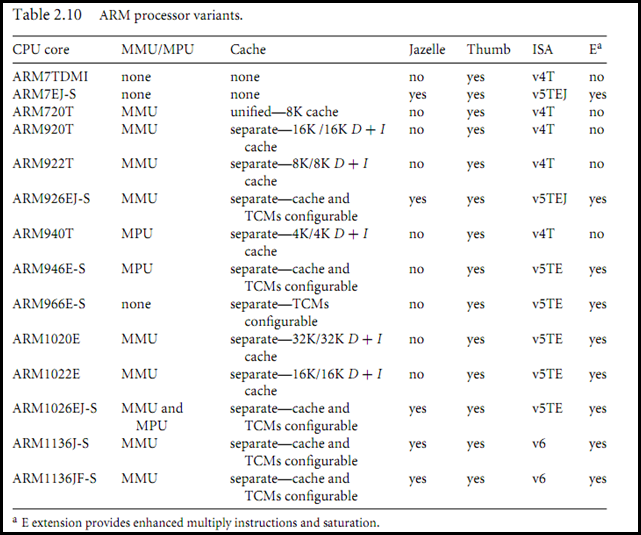

在每个系列中,存储器管理、Cache和TCM处理器扩展也有多种变化。ARM处理器的不同特性见下表:

2.8 总结

ARM处理器可以抽象成8个部件,ALU,barrel shifter,MAC,register file,instruction decoder,address register,incrementer and sign extend.

一个ARM处理器由一个内核及周围的组件并通过总线连接起来。内核扩展包括:

(a)Cache 可改善系统的总体性能。

(b)TCM 可提高效率并有确定性的实时响应。

(c)存储管理器用来管理存储器和保护系统资源。

(d)协处理器用来扩展指令和功能,协处理器15控制Cache、tcm和存储器管理。

3 异常和中断处理

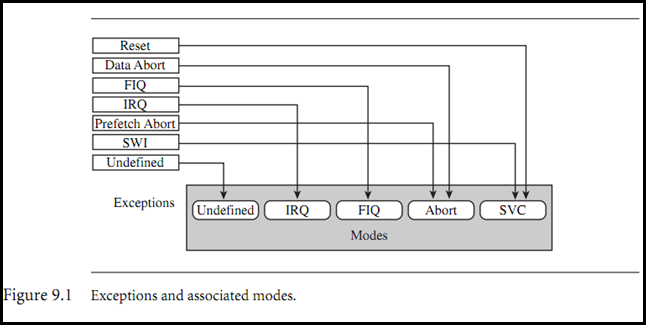

异常和中断处理时嵌入式系统的重要核心部分。它们负责处理中断、错误和其他外部系统触发事件。高效的异常处理能大大提高系统性能。ARM有7种中断或异常处理模式:reset、irq、fiq、SWI、data abort、prefetch abort、undefined instructions。

本章分3个部分:

异常处理:包括ARM处理器处理异常的一些特定细节。

中断:ARM把中断定义为一类特殊的异常,本节讨论了中断请求的使用。

中断处理方法:ISR。

3.1 异常处理

3.1.1 ARM处理器模式及异常

当一个异常导致模式改变时,内核自动地:(a)把cpsr保持到相应异常模式下的spsr。(b)把pc保存到相应异常模式下的lr。(c)设置cpsr为相应异常模式。(d)设置pc为相应异常处理程序的入口地址。

注意:当一个异常发生时,处理器总是切换到ARM状态。

3.1.2 向量表

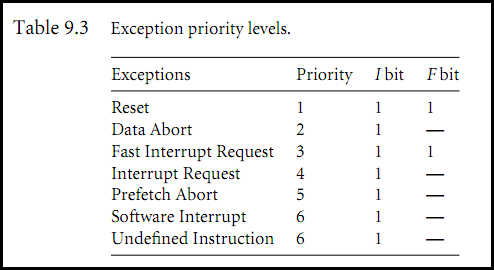

3.1.3 异常优先级

复位异常是优先级最高的异常,一旦复位信号产生,总是会发生复位异常。复位异常处理程序对系统进行初始化,包括配置存储器和Cache。外部中断源必须在IRQ或FIQ允许之前初始化,以避免还没有设置好相应的处理程序之前产生中断。复位处理程序还要为所有的模式设置堆栈指针。

在执行复位处理程序的前面几句,假设不会有别的异常和中断产生,除reset外所有异常均得不到处理,所以编程要避免SWI、undefined instruction以及存储器访问导致的异常。

Data Abort:发生在访问非法地址,如无效的存储器地址,或权限不允许的地址。由于没有禁止FIQ,在data abort的处理程序中,仍然为相应FIQ.当FIQ处理完后,会把控制权交还给data abort处理程序。

FIQ:FIQ发生在一个外设把内核的FIQ线置位uFIQ时。FIQ是优先级最高的中断。内核进入FIQ后,会自动禁止FIQ和IRQ,除非软件重新允许FIQ和IRQ,否则任何外部中断源都不能再次进入中端处理器。

IRQ:IRQ发生在一个外设把内核的IRQ线置为nIRQ时。FIQ和data abort都没有发生时,IRQ才能进入。进入IRQ后,内核禁止IRQ中断,直至当前中断源被清除。

Prefetch abort:发生在试图取指令导致的存储器访问失败。并且在没有优先级更高的异常发生时,才能进入。在进入相应处理程序后,内核会禁止IRQ,而允许FIQ.

SWI:发生在执行SWI指令且没有更高优先级异常产生时。进入后CPSR被设成管理模式。

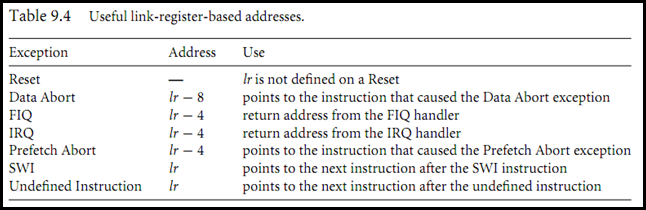

3.1.4 LR偏移

3.2 中断

ARM处理器有2中内核的中断:一是外设引起的硬中断,即FIQ和IRQ;一是软中断SWI。

本节重点放在FIQ和IRQ上,包括下列要点:(a)分配中断;(b)中断延迟;(c)IRQ和FIQ异常;(d)基本的中断堆栈设计实现

3.2.1 中断分配

系统设计时可以决定哪些硬件外设产生哪种中断请求。

中断控制器用于连接多个外部中断到ARM的FIQ和IRQ之一。复杂的控制器可以用编程来选择、决定一个外部源作为IRQ源还是FIQ源。

而SWI有点像LINUX的系统调用。

3.2.2 中断延迟

中断延迟指从外部中断信号发出,到第一条中断异常处理指令被取出。嵌入式系统通常对中断延迟要求严格。

中断延迟依赖于软件和硬件的组合。

软件通过2种方法缩短延迟:中断嵌套和中断优先级。

3.2.3 IRQ与FIQ异常

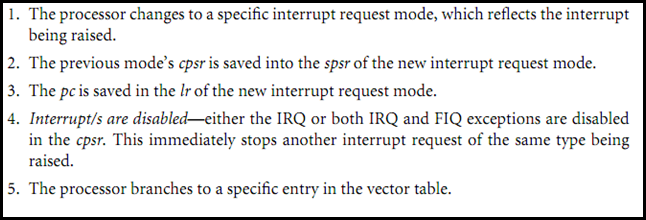

IRQ和FIQ异常执行流程为:

3.2.4 基本的中断设计与实现

异常堆栈的设计取决于以下因素:(a)操作系统需求,如允许中断嵌套的堆栈要求会比较大;(b)硬件平台存储空间的大小。

堆栈设计时,需明确2点:(a)位置,堆栈的起始位置以及采用何种增长方式;(b)堆栈大小。

避免内存溢出可以采用2种方法:(a)使用存储保护;(b)每个函数起始处检查SP。

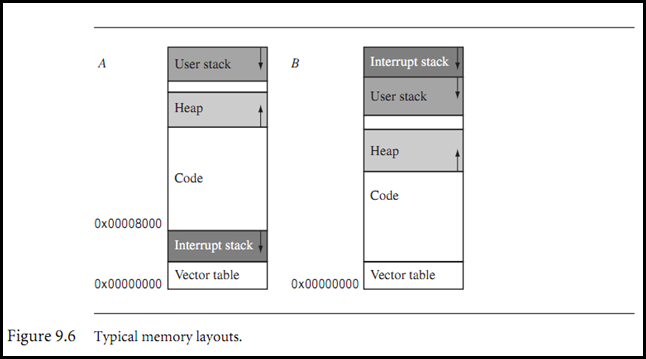

下图中,A是传统的中断堆栈设计方法,但B方案会优于A。因为B中断堆栈溢出后,不会破坏vector table,系统还有机会纠正自己错误。

3.3 中断处理方法

3.3.1 非嵌套中断处理

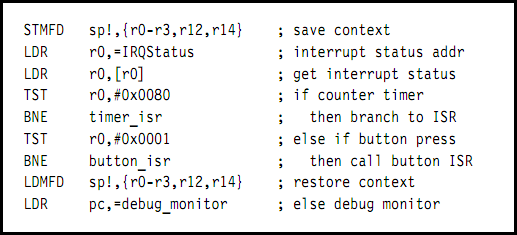

在进入中断处理程序,保护好上下文后,就必须确定中断源,因为会有多个外部中断源连接到IRQ上。一段确认外部中断源的示例程序如下:

3.3.2 嵌套中断处理

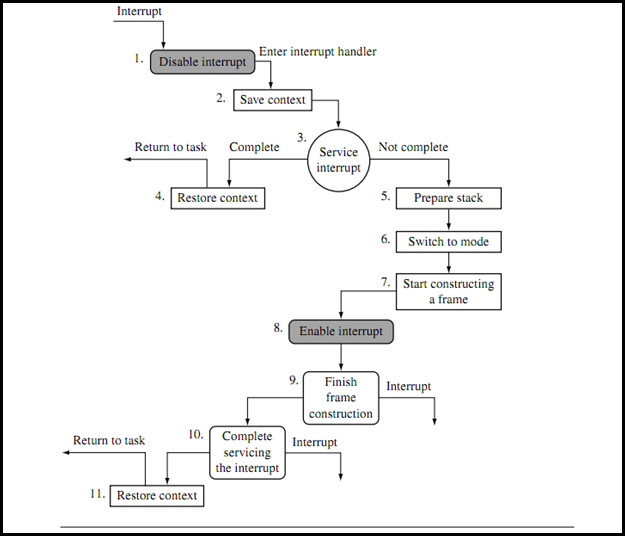

重新允许中断包括把IRQ模式切换到SVC或系统模式,在IRQ模式下,不能简单地重新允许中断,因为这可能会导致r14_irq被破坏。

执行上下文切换时包括清空IRQ堆栈,因为当IRQ堆栈还有数据时,处理器不会执行上下文切换。所有保存在IRQ堆栈的寄存器,必须转移至任务堆栈上,典型是放在SVC的堆栈上。然后,其余的寄存器也必须转移到任务堆栈上。他们被转移至一个叫做stack Frame的保留块。

Reference

《ARM嵌入式系统开发:软件设计与优化》

支付宝打赏

支付宝打赏  微信打赏

微信打赏